采用GaN LED倒装芯片的结构可以从根本上消除上述问题。图1-19 LED倒装芯片的结构示意图5.芯片键合技术光电子器件对所需要的材料在性能上有一定的要求,通常都需要有大的带宽差和在材料的折射指数上要有很大的变化。......

2025-09-29

1.引脚介绍

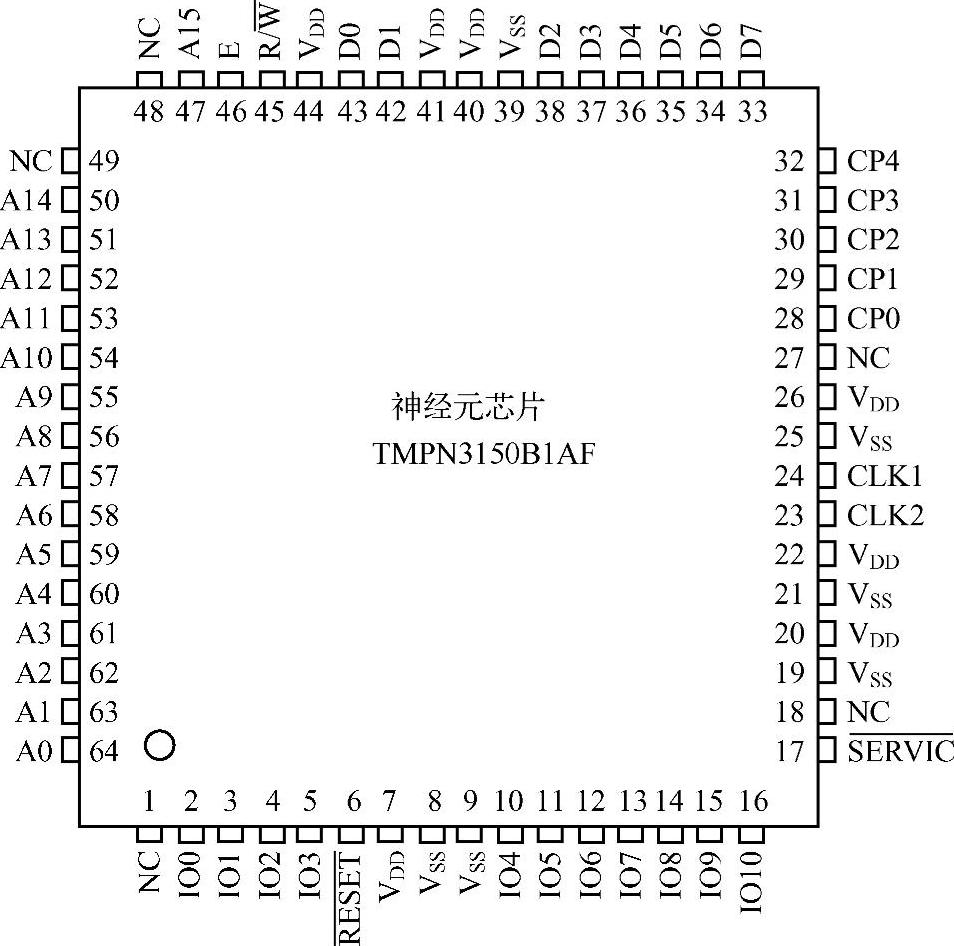

TMPN3150B1AF的引脚如图5-2所示。

图5-2 TMPN3150B1AF引脚图

引脚介绍如下:

CLK1:输入,连接振荡器或外部时钟输入。

CLK2:输出,连接振荡器。当外部时钟信息输入CLK1时,CLK2悬空(Open)。

I/O(内嵌上拉电阻),复位引脚(低态有效)。

I/O(内嵌上拉电阻),复位引脚(低态有效)。

I/O(内嵌可配置上拉电阻),服务引脚。工作期间指示灯输出。

I/O(内嵌可配置上拉电阻),服务引脚。工作期间指示灯输出。

IO0~IO3:I/O,大电流吸收能力(20mA)。通用I/O端口。

IO4~IO7:I/O(内嵌可配置上拉电阻),通用I/O端口。可指定IO4~IO7中的一个引脚为定时器/计数器1的输入;输出信号能传送到IO0;IO4可用作定时器/计数器2的输入引脚,此时IO1作为输出引脚。

IO8~IO10:I/O,通用I/O端口。可与其他器件串行通信。

D0~D7:I/O,用于扩充内存的数据总线。

输出,控制读/写的输出端口,以扩充内存。

输出,控制读/写的输出端口,以扩充内存。

E:输出,控制内存扩充的输出端口。

A15~A0:输出,扩充内存的地址输出端口。

VDD:输入,电源输入(典型值为5.0V)。

VSS:输入,电源输入(0V接地)。

NC:无任何连接。引脚悬空。

CP0~CP4:I/O,双向通信端口。通过指定模式支持一些通信协议。

2.CPU结构

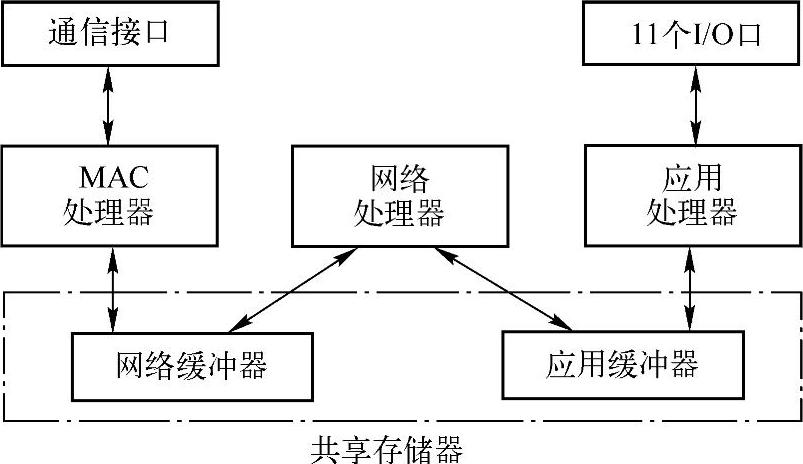

在神经元芯片内部有三个处理器:MAC处理器、网络处理器和应用处理器,三个处理器和存储器结构的框图如图5-3所示。

图5-3 Neuron芯片内部三个微处理器结构框图

MAC(Media Access Control)处理器完成介质访问控制,也就是LonTalk七层协议的1、2层,包括驱动通信子系统硬件和执行MAC算法。网络处理器完成LonTalk协议的3~6层,包括处理网络变量、寻址、认证、后台诊断、软件定时器、网络管理和路由等。同时,它还控制网络通信端口、物理地址发送和接收数据包。应用处理器完成用户的编程,包括用户编写的代码以及用户程序对操作系统的服务调用等。各处理器分别同时独立工作,通过缓冲器进行通信。网络处理器使用网络缓冲器和MAC处理器进行通信,使用应用缓冲器和应用处理器进行通信。

神经元芯片与现场设备的互联是通过它的11个I/O口实现的。这11个I/O口可以根据不同的需求配置成34种预编程设置,例如位输入、位输出、字节输入、字节输出、电平检测、并行I/O、多总线I/O、位移输入、位移输出、I2C、串行输入、串行输出、红外输入和脉冲计数输入等。其中,IO4~IO7可设置内部上拉电阻,IO0~IO3设置成大电流吸收(20mA,0.8V),IO0~IO10带有TTL标准的迟滞输入功能,IO0~IO7可设置为低电平检测锁存输入。通过11个I/O,借助于最小的外接电路,可灵活地实现输入输出功能。

神经元芯片为防止软件失效和存储器错误,包含三个Watchdog定时器(每个CPU一个)。如果应用软件和系统没有定时地刷新这些Watchdog定时器,整个神经元芯片将自动复位。Watchdog定时器的复位周期依赖于神经元芯片输入时钟的频率。当神经元芯片处于睡眠状态时,所有的Watchdog定时器被禁止。神经元芯片集强大的通信功能和现场采集控制功能于一体。因此,一个神经元芯片再加上几个现场传感器、执行器等外部器件,就是一个DCS系统中独立的控制单元。

神经元芯片有一个多功能通信端口(CP0~CP4),可支持不同的通信介质,可配置三种不同的接口模式,以适合不同的编码方案和波特率。单端模式是LON总线中使用最广泛的一种模式,单端和差分模式的数据编码和解码采用差分曼彻斯特编码(Differential Manches-ter Encoding)。

由于突破了通信介质的限制,因此LON总线可以根据不同的现场需要选择不同的收发器和通信介质。LON总线的收发器有双绞线收发器、电力线收发器、无线收发器和光纤收发器等。由于性能价格比的原因,最常用的是双绞线收发器以及电力线收发器。双绞线收发器有三种类型:直接驱动式、RS-485和变压器耦合,其中由于变压器耦合接口能满足系统高性能、高共模隔离和噪声隔离等多方面的需要,因此得到了广泛的应用。

3.存储器

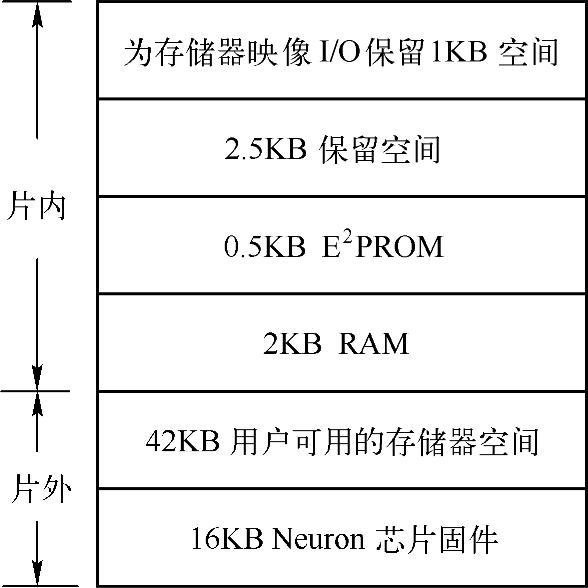

TMPN3150片内没有ROM,寻址空间为64KB,其中包括58KB的外部存储器及6KB的片内存储器,其存储器映像如图5-4所示。

图5-4 TMPN3150存储器映像

其中,0.5KB E2PROM中用来存储网络配置和网络寻址信息、48位的Neuron ID码和用户写入的应用代码及一般只读数据。RAM作为堆栈段数据区、应用和系统程序数据区、LonTalk协议应用缓冲区和网络缓冲区。在外部存储器中,16KB用来存储LON操作系统,剩下的空间可作为用户编写的应用代码和应用程序所需要的额外数据区、应用缓冲区和网络缓冲区。外接存储器可以扩展FLASH、ROM、E2PROM、SRAM以及它们的组合,以256B递增。

4.时钟信号

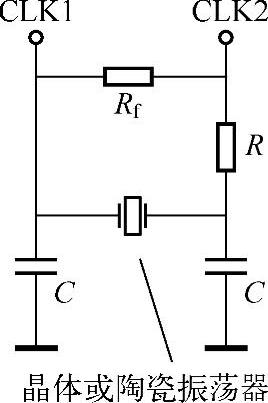

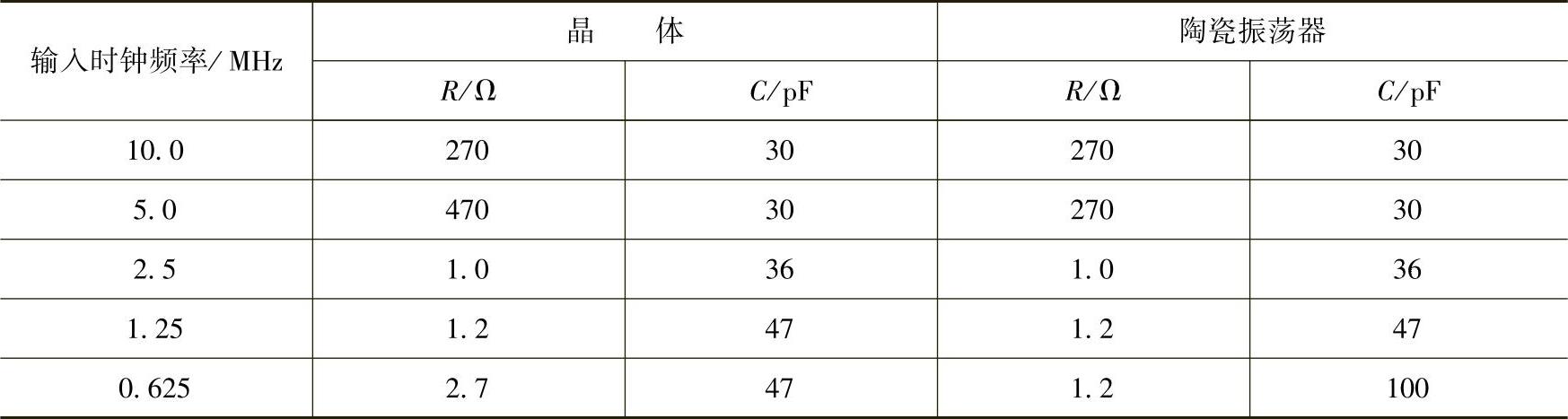

Neuron芯片有一振荡器使用外接晶体或陶瓷共振器电路来产生输入时钟CLK1。对低功耗的应用,Neuron芯片输入时钟频率范围可在625 kHz~10 MHz之间。有效输入时钟频率是10 MHz、5 MHz、2.5 MHz、1.25 MHz和625 kHz。还有一种方法用来获取输入时钟,这就是外部产生时钟信号驱动Neuron芯片上符号是CLK1的CMOS输入引脚,此时符号为CLK2的引脚必须悬空或用来驱动最多一个外部CMOS负载。时钟频率的准确度为±1.5%或更精确以确保各节点能比特同步。图5-5给出时钟产生电路,表5-2给出构成时钟产生电路的元器件值。

图5-5 时钟信号产生电路

表5-2 时钟产生电路的元器件值

注:1.电容值包括寄生电容。晶振及陶瓷谐振器的生产商可建议其他电容值。

2.Rf=100kΩ。对陶瓷谐振器Rf是必需的,对晶体则可要可不要。

3.晶体或陶瓷谐振器的频率=输入时钟频率。

4.晶体可并联或串联谐振。建议使用NPO型陶瓷电容。电阻和电容的准确度是±5%。

Neuron芯片以2的幂实现输入时钟的分频,从而获得芯片的系统时钟。系统时钟再4分频,为应用I/O、网络通信端口以及CPU的看门狗定时器提供时钟信号。

5.休眠/唤醒电路

(1)休眠电路

Neuron芯片在软件控制下可进入低功耗的休眠状态。在这种状态下,振荡器、系统时钟、通信端口以及所有的定时器/计数器都关闭,但所有的状态信息包括片上RAM的内容仍然保留。

(2)唤醒电路

当检测到唤醒事件时,Neuron芯片将允许振荡器起振并等待进入稳定状态,完成内部维护后恢复操作。(https://www.chuimin.cn)

6.看门狗定时器

Neuron芯片有三个看门狗定时器,每个CPU一个。用途是防止存储器故障或软件出错。如果应用或系统软件未能周期地复位这些定时器,整个Neuron芯片将自动复位。在输入时钟频率为10 MHz时,看门狗的时间周期将近为0.84s,并与输入时钟速率成反比,即输入时钟速率越高,看门狗的时间周期越长。当Neuron芯片处在休眠状态时,所有的看门狗定时器都将关闭。

7.复位

复位引脚是漏极开路、双向且低有效的I/O引脚,内部有一个电流源充当上拉电阻。使复位引脚有效的方法有两种:

1)外部信号驱动产生低电平输出。

2)内部控制产生低电平输出。

引起复位引脚复位的内部控制有以下几种:

1)软件(应用程序或网络复位消息)。

2)看门狗定时器时间溢出。

3)低压检测。

当复位引脚回到高电平,Neuron芯片开始初始化,初始化程序的启动地址是0x0001。在设定初值的过程中,所有的输出引脚处在高阻状态,直到初值设定完成才开始处理应用程序。

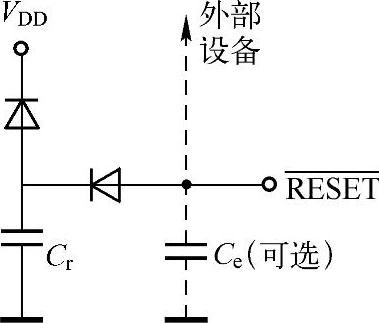

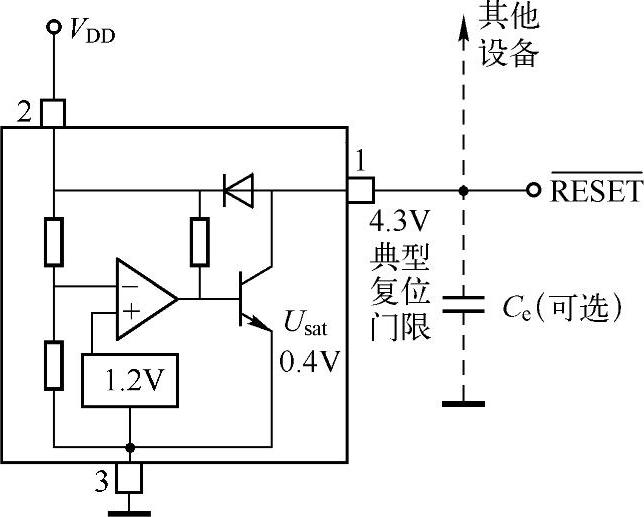

(1)复位电路

Neuron芯片外接复位电路是为满足特定的应用需要,例如存储器接口设计对复位电路的特殊要求,有些收发器也会将其某些额外的要求放在外接的复位电路上来实现。

图5-6描述的是在保证Neuron芯片可靠工作的条件下,最简单的外接复位电路。有些Neuron芯片内部带有LVI电路,对这类芯片是否仍需要外接LVI电路,取决于应用的需要。如果不能确保应用所使用的电源性能良好,最好还是使用外接LVI电路。

对图5-6的复位电路在此不详述。这里主要介绍一种带有外接LVI电路的复位电路,如图5-7所示。图中Ce为可选外部复位电容。因为复位引脚是双向的,在软件的控制下也可输出有效低电平对外部设备(如收发器)实现复位,所以在这种情况下电容Ce是必不可少的。

图5-6 外接复位电路

图5-7 外接LVI的复位电路

LVI电路在此的作用是在系统电源出现电压抖动或未完全掉电的情况下,检测电源电压VDD是否低于规定的工作电压,若是,该电路将下拉复位线至低电平,Neuron芯片重新初始化。

由于Neuron芯片复位引脚是双向的,LVI电路必须是集电极开路或漏极开路输出。如果LVI驱动使得复位引脚为高电平,在软件复位期间Neuron芯片将不能可靠地判断复位引脚是否为低电平。Neuron芯片复位引脚的这种不确定性将引起一些有违常规的现象发生,如节点出现非应用(Applicationless)错、Neuron芯片的复位电路损坏等。在复位引脚会受ESD(静电放电)影响的应用中,应增加一恰当的外部保护电路,即串一个300Ω左右的电阻。

LVI集成芯片可选用Dallas公司的DS1233集成芯片。

(2)复位处理

在复位期间,I/O引脚、通信端口以及服务引脚都处在高阻状态。

在复位引脚释放后,Neuron芯片允许在执行应用程序之前振荡器起振、稳定并完成软硬件的初始化。振荡器起振后进入稳定的这段时间,Neuron芯片允许输入时钟周期最多出现15次跃变。固件初始化要完成几项任务来初始化Neuron芯片,从而保证它的完整性。这几项任务是:

1)振荡器起振。

2)振荡器稳定。

3)栈初始化以及内建的自检测。

4)服务引脚初始化。

5)状态初始化。

6)片外RAM的初始化。

7)随机数触发数据的计算。

8)系统RAM设置。

9)通信端口初始化。

10)校验和初始化。

11)秒定时器初始化。

12)调度初始化。

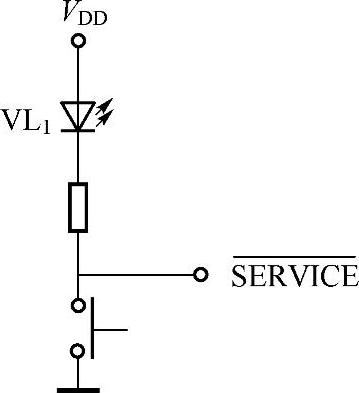

8.服务引脚

服务引脚输入和漏极开路输出交替,频率是76Hz,波形占空比是50%。当其作为输出时,它能吸收20mA电流用于驱动一LED;当其用作输入时,它有一个可选的片内上拉电阻使输入能被拉高为高电平而进入无效状态。当然这只在LED与上拉电阻之间未连接时才使用。在Neuron芯片固件的控制下,该引脚主要用在节点配置、安装以及维护等过程中。例如,当节点还未配置网络地址信息时,LED闪烁,频率是0.5Hz。当服务引脚接地时,节点会在网上发送一含有Neuron芯片ID值的网络管理消息,网络管理设备将使用该消息中包含的信息来安装及配置该节点。

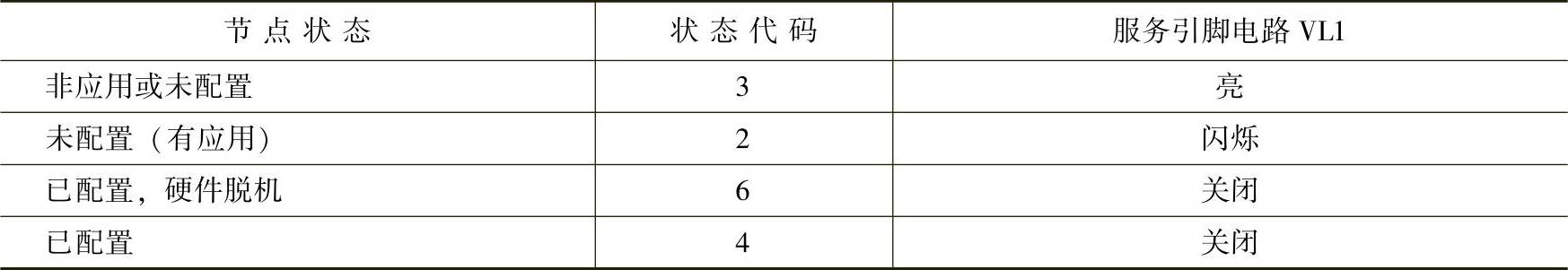

典型的服务引脚电路如图5-8所示。表5-3示出了电路上发光二极管VL1的状态。复位时,服务引脚的状态不确定,服务引脚的上拉电阻默认是使能。

图5-8 服务引脚电路

表5-3 服务引脚的状态

9.定时器/计数器

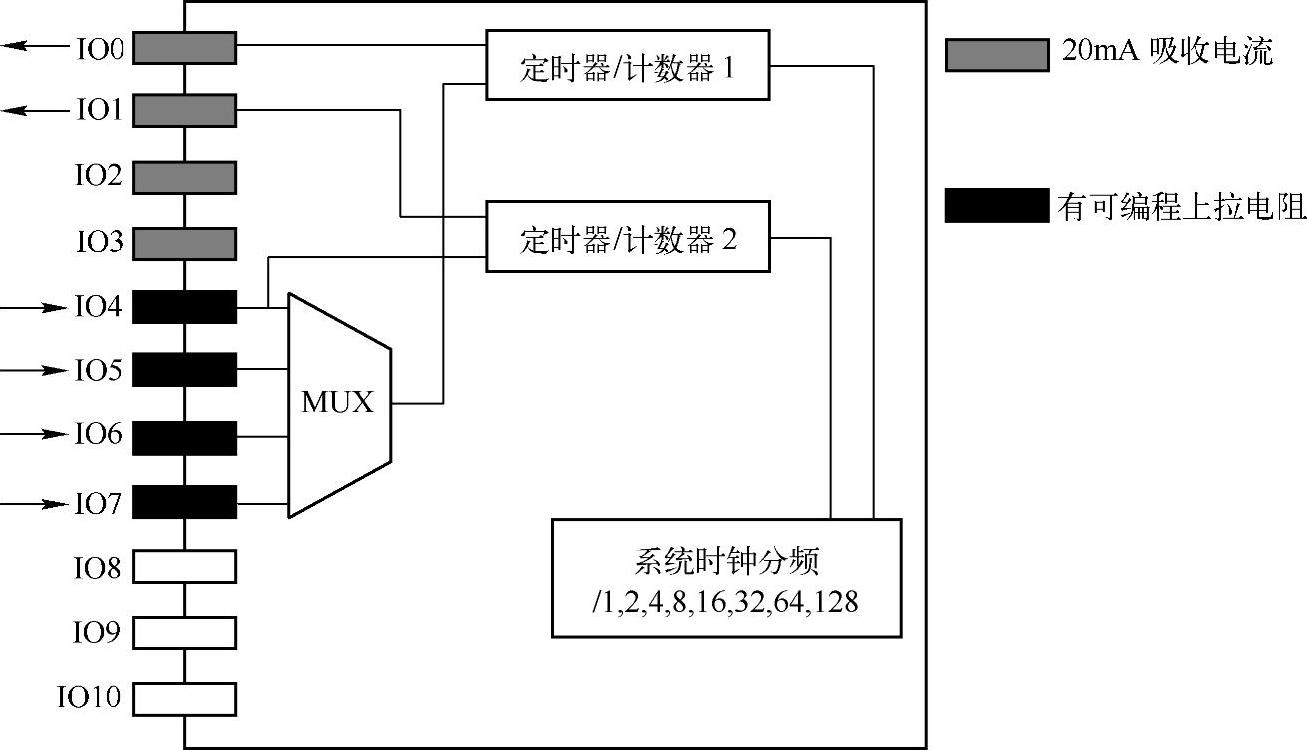

Neuron芯片上有两个16位的定时器/计数器,即定时器/计数器1和定时器/计数器2。定时器/计数器1又可称为多路复用定时器/计数器,因为该定时器/计数器的输入引脚可通过一个可编程多路转换器MUX在IO4~IO7中选择。它的输出连接引脚IO0。定时器/计数器2称为专用定时器/计数器。它的输入连接引脚IO4,输出连接引脚IO1。定时器/计数器与应用指定的外部硬件的连接图如图5-9所示。

图5-9 定时器/计数器与应用层硬件设备连接

相关文章

采用GaN LED倒装芯片的结构可以从根本上消除上述问题。图1-19 LED倒装芯片的结构示意图5.芯片键合技术光电子器件对所需要的材料在性能上有一定的要求,通常都需要有大的带宽差和在材料的折射指数上要有很大的变化。......

2025-09-29

接下来我们以ADA01芯片和ADA01AL芯片为例,讲述其工作性能。ADA01芯片引脚描述。ADA01AL芯片性能参数① 典型工作电压:2.4~5.5V。......

2025-09-29

水平放置的MFD顶部有7个PDP,两侧各有6个PDP;竖直放置的地图显示器顶部有6个PDP,两侧各有10个PDP。所有的MFD都采用触摸屏,也可以通过光笔、键盘、手柄上的拇指光标控制器进行交互。车长主要通过MFD完成任务,也可通过字母/数字键盘、可编程显示按钮、拇指光标控制器和4个方向按键与坦克进行交互。......

2025-09-29

本节介绍某贴脚芯片实体建模范例,在该范例中主要应用到“长方体”“矩形”“多段线”“圆角”“扫描”“UCS”“三维对齐”“矩形阵列”“三维镜像”和“差集”等工具命令。图9-74 某贴脚芯片实体模型图9-74 某贴脚芯片实体模型在“快速访问”工具栏中单击“新建”按钮,弹出“选择样板”对话框,选择“acadiso3D.dwt”,单击“打开”按钮。......

2025-09-29

据估算,建造一个芯片制造厂,需要花费150亿美元,等同于一个美国尼米兹级核动力航空母舰编队的造价,而这还只是芯片厂的前期投资。摩尔定律不断得到验证,导致了另一个结果,那就是芯片行业天然会随着技术进步发生自我贬值。从倪光南的“方舟一号”,到邓中翰的“星光一号”,再到展讯的第一枚手机芯片,在全国产业竞争快速迭代的赛道上,中国选手没有跑赢摩尔定律,最终先后被市场拉下马来。......

2025-09-29

下面从应用的角度,对在选择ARM芯片时应考虑的主要因素做详细说明。2.系统时钟控制器系统时钟决定了ARM芯片的处理速度。3.内存容量在不需要大容量存储器时,可以考虑选用有内置存储器的ARM芯片。某些特殊应用ARM芯片没有外部扩展功能,如德国Micronas公司的PUC3030A。14.UART和IrDA绝大部分ARM芯片具有1~2个UART接口,可以用于和PC通信或用Angel进行调试。15.DSP协处理器具有DSP+ARM结构的ARM芯片对图像、视频、多媒体等数据具有很好的处理效果。......

2025-09-30

我们测试两种焊料凸点并比较它们的电迁移现象。第一次回流在把焊料凸点印刷在芯片上后完成,第二次回流是为了组装芯片和印刷线路板。为了对焊料凸点电迁移进行实时观测,在电迁移测试之前,我们采用机械和化学方法将一对焊料凸点切为截面并抛光。为了可以进行观察,要时常暂停电迁移试验,所以观察是不连续的且在不同的时间下重复进行的。图9.8观察电迁移时所用倒装芯片焊点两个横截面的原理......

2025-09-29

ICEIQS01电路控制集成块主要由比较器、触发器、锁存器、数字处理模块、输出缓冲器等电路组成,图4-37a为内部结构框图。软启动触发器和通断开关器,是处理电路在待机和瞬态电压冲击时应急处理电路。脉冲锁定触发器的输出连接到开通时间触发器,它执行电路锁定后待机,等到下个触发脉冲启动IC,经过7脚内的输出缓冲器输出触发脉冲,电路开始工作。图4-37b是ICEIQS01引脚排列图。......

2025-09-29

相关推荐