如图6.34所示,时钟周期定义为10ns,按设计规格,加法器的延迟为6个时钟周期。图6.34 多时钟电路设计如图6.35所示,DC将会仅仅在第6个时钟上升沿,即60ns处,建立时序分析。图6.36 多时钟保持时间约束保持时间将会提早5个时钟周期,所以加法器d允许延迟为Thold<加法器允许的延迟<60-Tsetup。图6.37是另一个多时钟周期的例子,图中乘法器运算为2个时钟周期,加法器运算为1个时钟周期,其约束为图6.37 多时钟电路设计......

2023-06-26

图6.10中提到了4种时序路径,分别是寄存器间的路径、输入路径、输出路径和组合逻辑路径。接下来我们对这4种路径的时序约束逐一进行介绍。首先寄存器间的路径可以通过约束时钟来实现。

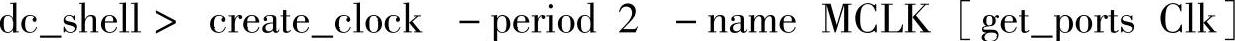

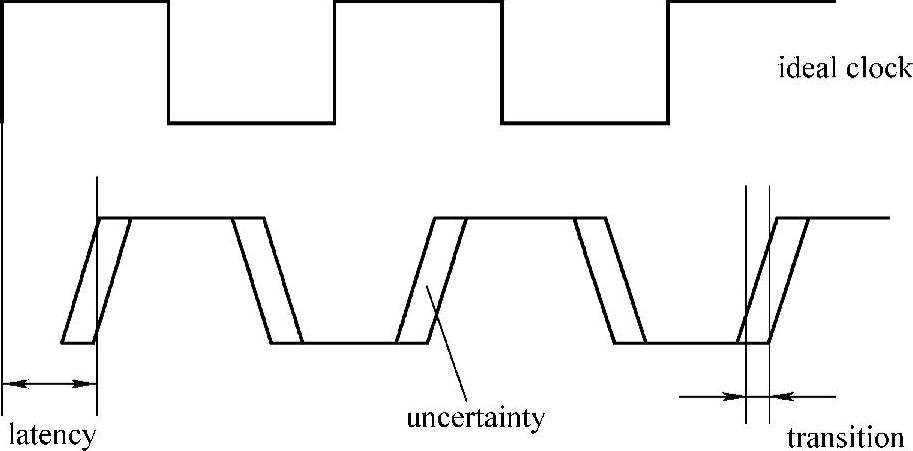

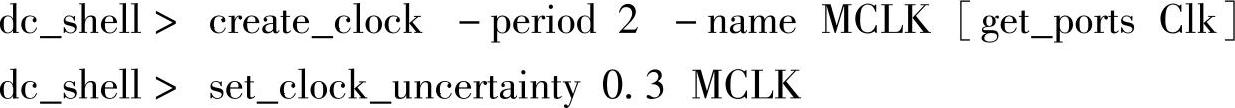

如图6.14所示,寄存器之间存在组合逻辑X,寄存器FF3的建立时间为0.2ns,可通过下面这条命令,将一个周期为2ns所示时钟施加在端口Clk上,并取名为MCLK(命令中的2表示2个时间单位,时间单位在技术库中定义,此例中时间单位为1ns,后文中的命令也类似)。

通过这条约束命令,DC可以计算出X逻辑的最大延迟为2ns-0.2ns=1.8ns。如果X逻辑延迟超过1.8ns,则寄存器FF3采到的值为亚稳态,所以DC会尽力综合将X逻辑的延迟限制在1.8ns以内,在满足时序约束的前提下,DC会保证电路的功耗和面积尽可能小。

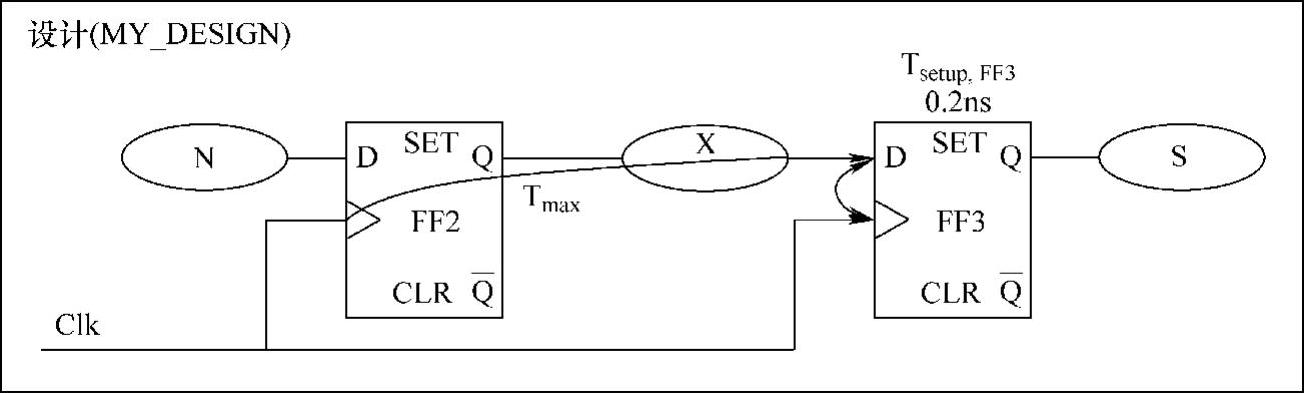

寄存器时钟端的时钟由于经过了前级时钟树的各种器件的作用,波形已经不再是理想时钟,没有那么规则,如图6.15所示。所以在考虑时钟约束的时候要考虑到它的uncertainty、latency和transition。

图6.14 寄存器间的时序路径

图6.15 理想时钟与实际时钟

uncertainty描述的是时钟跳变时间的不确定性,这种不确定性来源于3个方面,分别是jitter、skew和margin。jitter指的是时钟源的抖动,skew是指不同寄存器始终端口之间的时钟偏差,margin指的是工程余量。时钟的uncertainty可以通过set_clock_uncertainty命令设置,下例接图6.14进行说明。

由于时钟存在不确定性,所以对X逻辑的约束较为苛刻,即允许X逻辑的最大延迟为2ns-0.3ns-0.2ns=1.5ns。

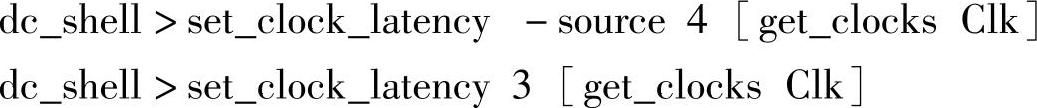

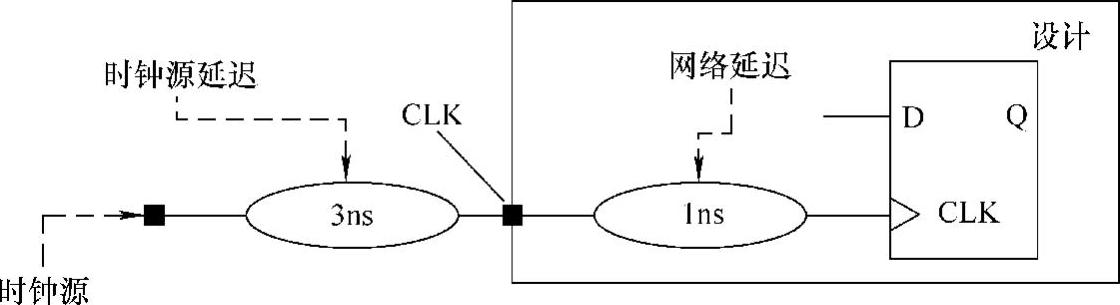

latency指的是时钟沿到来的延迟。为了平衡时钟到达不同寄存器之间的延迟,在时钟树上要加入缓冲器(buffer),这些buffer延迟加上线延迟就产生了latency。latency分为两种,一种是时钟源到被综合模块时钟端口之间的延迟,叫作Source Latency。另一种是被综合模块时钟树上的延迟,叫作Network Latency。set_clock_latency命令默认设置是Network Latency,如要设置Source Latency可加选项-source,如图6.16所示。

图6.16 Clock Latency

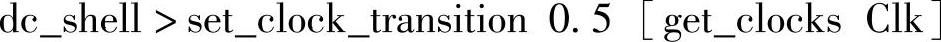

时钟的跳变沿在实际电路中并不是瞬时变化的,而是有一定的坡度,transition描述的就是这个坡度的持续时间,如下例所示。

有关CMOS集成电路EDA技术的文章

如图6.34所示,时钟周期定义为10ns,按设计规格,加法器的延迟为6个时钟周期。图6.34 多时钟电路设计如图6.35所示,DC将会仅仅在第6个时钟上升沿,即60ns处,建立时序分析。图6.36 多时钟保持时间约束保持时间将会提早5个时钟周期,所以加法器d允许延迟为Thold<加法器允许的延迟<60-Tsetup。图6.37是另一个多时钟周期的例子,图中乘法器运算为2个时钟周期,加法器运算为1个时钟周期,其约束为图6.37 多时钟电路设计......

2023-06-26

如图6.27所示,图中有多个时钟,但这些时钟都是来自同一个时钟源。分别由3GHz的时钟通过9分频、6分频、4分频和3分频得到了CLKA、CLKC、CLKD和CLKE。图6.27 多时钟同步设计CLKC在被综合的模块中有对应的端口,则其定义就与单时钟一样,即:由于CLKA、CLKD和CLKE在要综合的模块中没有输入端口,因此需要使用虚拟时钟。图6.30 多时钟同步输出约束DC会找出波形上升沿间隔的多种情况,然后按照最严格的情况进行综合约束。......

2023-06-26

约束又称联系,它是体系中构件之间或者体系与基础之间的连接装置。一种约束装置的约束数等于它使体系减少的自由度数。常见的约束类型有链杆、铰、刚性连接。连接n个刚片的复铰具有2(n-1)个约束。或者说,三个刚片原来共有9个自由度,由于复铰A起着两个单铰的作用,减少了4个自由度,所以,体系最后为5个自由度。因此,一个刚性连接相当于三个约束,能减少三个自由度。图11-8所示的固定端约束也是刚性连接。......

2023-06-16

图4-30所示为AVR的主要时钟系统及其分布,这些时钟并不需要同时工作。终止CPU时钟将使内核停止工作和计算。I/O时钟还用于外部中断模块。此时钟通常与CPU时钟同时挂起或激活。......

2023-06-26

下面对工程中一些常见的码约束进行分类分析,并归纳出其反力特点。因此,柔性约束产生的约束反力总是通过接触点、沿着柔性体中心线而背离被约束的物体。链条或胶带绕在轮子上时,对轮子的约束反力沿轮缘切线方向,如图1-8所示。固定铰支座的结构简图及其约束反力如图1-10所示。由于这种约束只限制了竖直方向的运动,因此,其约束反力沿滚轮与支承接触处的公法线方向,指向被约束构件。......

2023-06-16

图6.2所提算法与其他算法的MSE性能比较由于完美信道为非完美信道下更能展现算法性能的一个特例情况,因此首先对于完美信道下的中继混合预编码设计进行仿真分析。图6.6中继接收与发送采用不同量化位时SE随量化位数变化曲线图6.7显示了利用不同分辨率PSs时的EE性能。这是因为与3位分辨率的情况相比,具有1位分辨率PSs的可实现SE的退化是显著的。......

2023-08-23

时钟树综合前的时钟网络如图8.27所示,呈发射状。为了平衡寄存器到时钟端口的延时,时钟树综合通过许多专用的时钟缓冲单元来搭建平衡的网状结构。也就是基于如上原因,时钟树综合这一步骤在数字物理设计流程中,一般在布局完成后进行。具体到Encounter工具,Encounter的时钟树工具现在版本使用的有两个时钟树综合引擎,两者均有读入SDC约束的能力。......

2023-06-26

针对切削液的环境污染,各国都制定了相关的法律。切削液在生产成本中所占的比例已经达到了13%~17%,而且切削液的排放严重污染了土壤、大气和水资源,使人们的生活环境质量下降并危害身心健康。切削液的污染治理问题,也应该从源头抓起,在切削过程中尽量少用或者不用切削液,实施干切削,从源头切断污染源,是加工制造业实践可持续发展战略的根本性措施。......

2023-06-25

相关推荐