(一)焊条的组成及作用焊条就是涂有药皮的供焊条电弧焊使用的熔化电极,它是由药皮和焊芯两部分组成的。在尾部有一段裸焊芯,约占焊条总长1/16,便于焊钳夹持并有利于导电。此外,加入铁粉可以提高焊条熔敷效率,但对焊接位置有影响。型号编制方法 焊条型号由四部分组成:①第一部分用字母“E”表示焊条。......

2025-09-29

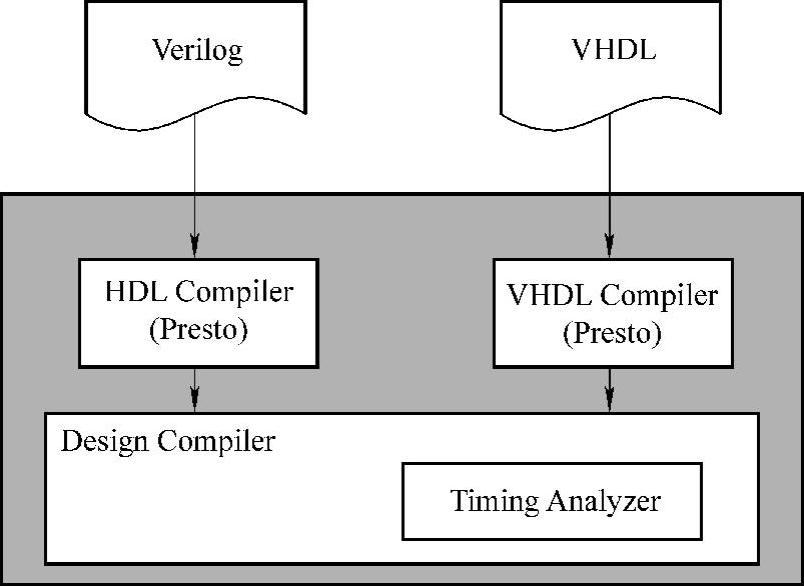

在进行综合时,DC用内建的静态时序分析工具Design Time来估算路径的延迟以指导优化,并用Design Time来产生时序报告,如图6.9所示。

图6.9 DC的静态时序分析

静态时序分析可以不通过动态仿真就确定电路是否满足时间的约束。静态时序分析主要包括3个主要步骤。

1)把设计分解成时间路径的集合;

2)计算每一条路径的延迟;

3)所有的路径延迟都要做检查,把它与时间的约束比较,看它们是否满足约束的要求。

DC通过下面的方法把设计分解为时序路径的集合。每条路径都有一个终点和一个起点。

起点:

◆除了时钟以外的输入端口;

◆时序器件的时钟端口。

终点:

◆除了时钟以外的输出端口;(https://www.chuimin.cn)

◆时序器件除时钟端口外的其他输入端口。

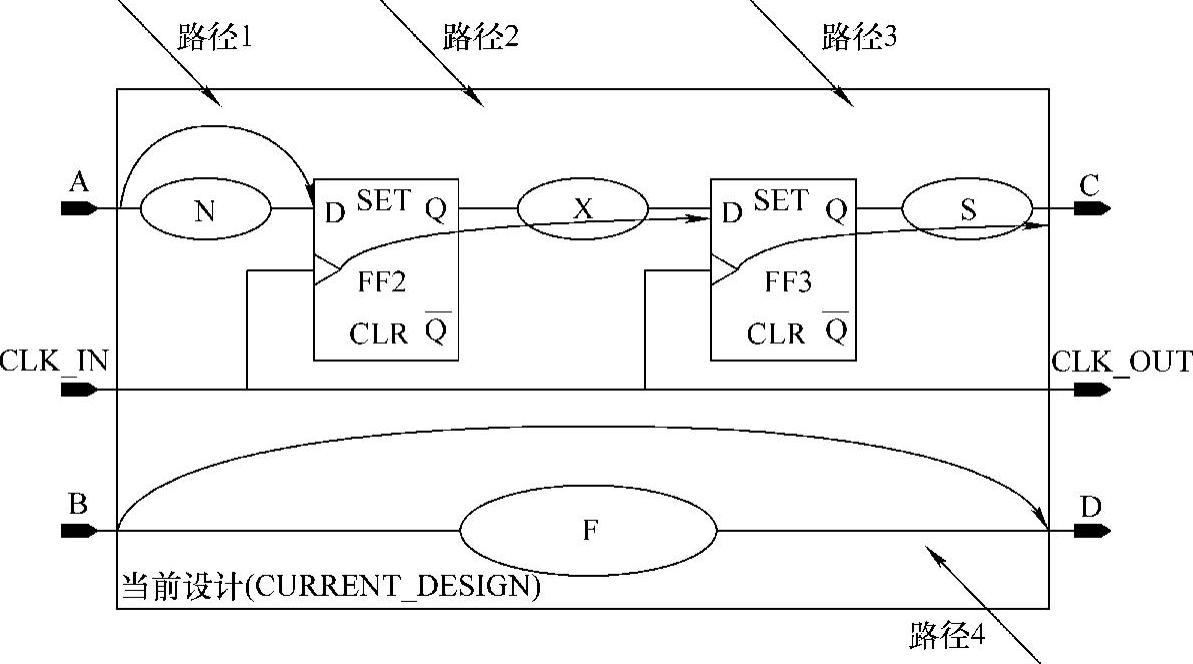

如图6.10所示,CURRENT_DESIGND的时序路径的起点有A、B、FF2/CLK_IN和FF3/CLK_IN,终点有C、D、FF2/D和FF3/D。将这些起点和终点连在一起可以得到4条时序路径,分别为path1、path2、path3和path4。

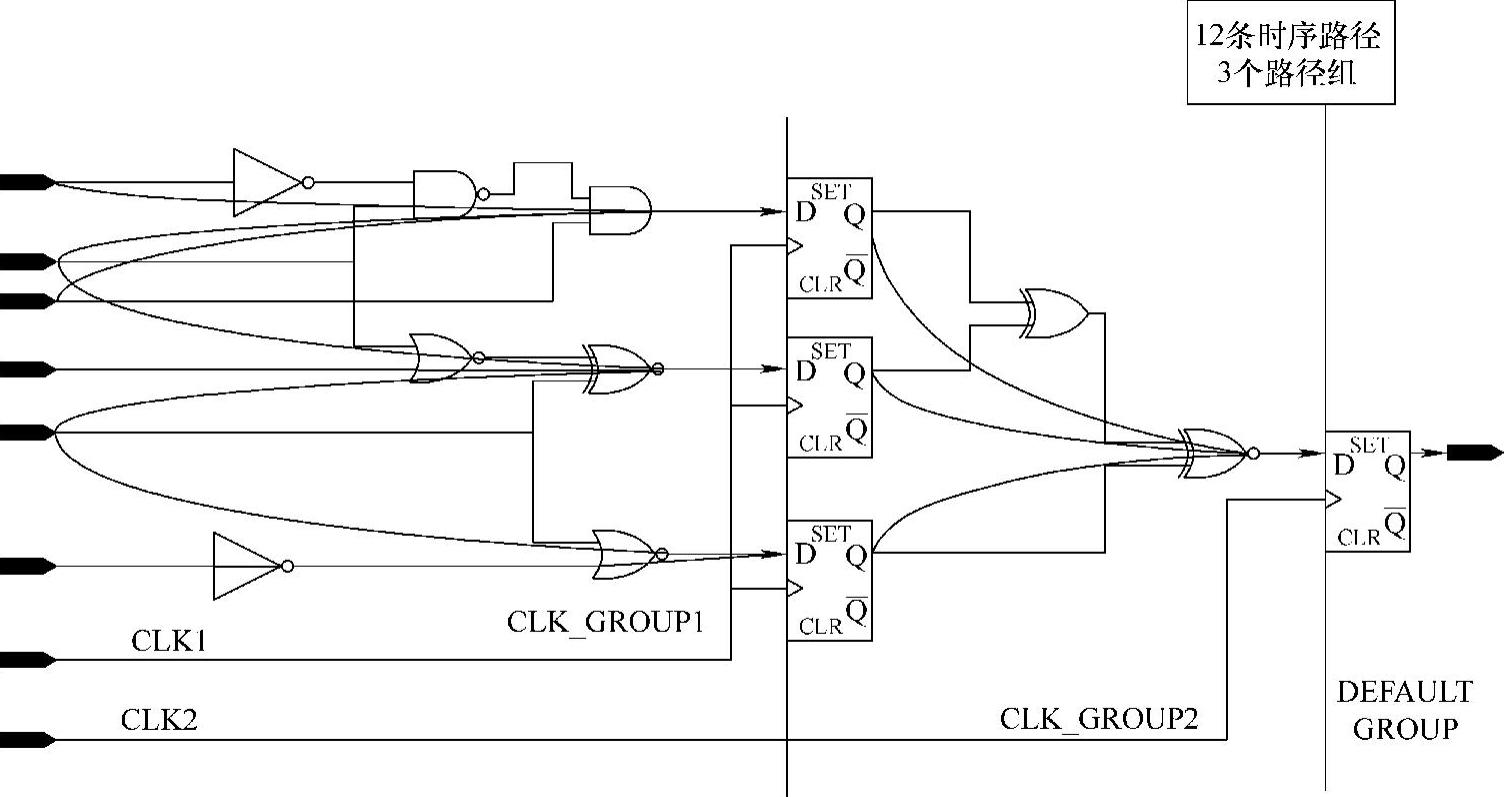

为了便于分析时序,时序路径又被分组。路径按照终点控制它的时钟进行分组,如果路径不被时钟控制,这些路径被归类为默认路径组。我们可以用report_path_group命令来报告当前设计中路径分组情况。

图6.10 时序路径

如图6.11所示,图中共有5个终点,CLK1控制3个终点,共有8条路径。CLK2控制一个终点,共有3条路径。输出端口为一终点,它不受任何时钟控制,只有一条路径,属于默认组。这12条路径被分为3个路径组分别是CLK1、CLK2和默认路径组。

图6.11 时序路径组

在计算路径延迟时,DC把每一条路径分成时间弧,时间弧描述单元或连线的时序特性。单元的时间弧由工艺库定义,包括:

◆单元的延迟;

◆时序检查(触发器的setup/hold检查、clk→q的延迟等)。

连线的时间弧由网表定义。路径的延迟与起点的边沿有关,图6.12中,假设连线延迟为0,如果起点为上升沿,则该条路径的延迟等于1.5ns。如果起点为下降沿,则该条路径的延迟为2.0ns。这说明单元的时间弧是边沿敏感的。

相关文章

(一)焊条的组成及作用焊条就是涂有药皮的供焊条电弧焊使用的熔化电极,它是由药皮和焊芯两部分组成的。在尾部有一段裸焊芯,约占焊条总长1/16,便于焊钳夹持并有利于导电。此外,加入铁粉可以提高焊条熔敷效率,但对焊接位置有影响。型号编制方法 焊条型号由四部分组成:①第一部分用字母“E”表示焊条。......

2025-09-29

可持续发展状况的静态评价方法,是在建立的都江堰灌区可持续发展的评价指标体系结构基础上,利用层次分析法确定各评价指标的权重,进而求算都江堰灌区的“可持续发展度A”、“水资源开发利用可持续度B1”和“社会经济可持续度B2”。......

2025-09-29

熔断器是一种简单而有效的一次性保护电器。螺旋式熔断器螺旋式熔断器是机床上使用较多的熔断器,在它的熔体上端带有熔断指示器,当熔体熔断时指示器自动脱落,可透过瓷帽上的玻璃孔观察到。5)熔断器的额定分断能力必须大于电路中可能出现的最大故障电流。6)若使用新型熔断器时,应参照其有关说明书进行选择。图1-37 熔断器的图形和文字符号......

2025-09-29

原型制图应用临摹使学生获得了对原型结构应用的初步认知,款式结构分析与改造制图,能够为学生深入学习服装结构设计做更好的铺垫。如对原图进行款式不变、按标准号型尺寸的改造,可通过肩宽、胸、腰、臀三围的缩减,省、分割位置及袖窿深浅的控制调整等,进行款式结构改造的原型制图。......

2025-09-29

随着轿厢继续下行,限速器轮槽与限速绳索之间产生摩擦力使限速绳被轧住,带动安全钳联动系统,将安全钳拉杆提起,安全钳楔块动作,轿厢被制动在导轨上。限速拉簧调节螺栓的拉力,可调节限速器的动作速度。当限速器动作后需要复位时,可以将轿厢慢速上行,限速轮反向旋转,棘爪与棘轮脱开,安全钳即可复位。......

2025-09-29

回火的主要目的是为了减少或消除淬火内应力,获得所需的组织,改善力学性能。与淬火马氏体相比,回火马氏体既保持了钢的高硬度、高强度和良好的耐磨性,又适当提高了韧性。习惯上将淬火与高温回火相结合的热处理方法称为调质处理。......

2025-09-29

当原子的跃迁距离为3×10-10 m时,驱动力所做的功为Δw=4.8×10-27 N·m=4.8×10-27 J,这个结果与我们理论计算出的热迁移时的热能改变量非常接近。因此如果电流密度104 A/cm2可在焊料接头中引起电迁移现象,那么在1 000℃/cm温度梯度下,焊料接头中也能发生热迁移。为了测出Q*,当知道原子通量时,可使用原子通量方程式,并在扩散系数、温度梯度和平均温度已知的情况下计算出Q*。在12.2.4节中,铅原子在热迁移中的转移热已通过使用式被估测出来了。......

2025-09-29

(一)引纬的作用引纬是以引纬器或高速射流将纬纱引入梭口,与经纱形成交织。(二)引纬的方式1.有梭引纬 梭子内装有携带一定数量纬纱的纡子,在左右投梭棒的交替打击下在梭口内循环往复运动,带引纬纱穿越梭口、绕( 折) 返布边,即为梭子引纬。我国目前仍有一定数量织机在使用这种引纬方式。采用无梭引纬方式的织机被称为无梭织机,其按引纬方式不同可划分为喷气织机、喷水织机、剑杆织机和片梭织机。......

2025-09-29

相关推荐