如图10-6所示为PROFIBUS电缆,包括100%的铝箔屏蔽和65%的镀锡铜编织网屏蔽,具有最大的屏蔽效果。图10-11 总线连接器的终端电阻图10-12 终端电阻的具体设置5.通信处理器与PROFIBUS相关联的通信处理器主要包括:1)CP 342-5通信处理器;2)CP 342-5 FO通信处理器;3)CP 443-5通信处理器;4)用于PC/PG的通信处理器。......

2025-09-29

本节讲述ATmega48/88/168的存储器。AVR结构具有两个主要的存储器空间:数据存储器空间和程序存储器空间,此外,ATmega48/88/168还有EEPROM存储器以保存数据,这三个存储器空间都为线性的平面结构。

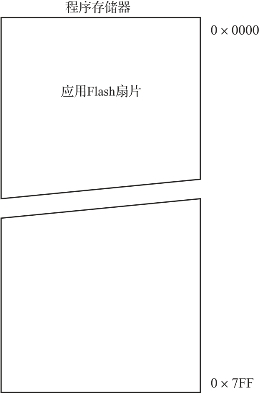

ATmega48/88/168具有4/8/16 KB的在线编程Flash,用于存放程序指令代码。因为所有的AVR指令为16位或32位,故Flash组织成2/4/8 KB×16。对于ATmega88与ATmega168,用户程序的安全性要根据Flash程序存储器的两个区:引导(Boot)程序区和应用程序区分开来考虑。ATmega48中没有分为引导程序区和应用程序区,SPM指令可在整个Flash中执行。存储器至少可以擦写10 000次。ATmega48/88/168的程序计数器(PC)为11/12/13位,因此可以寻址2/4/8 KB的程序存储器空间,如图4-22所示。

1.SRAM数据存储器

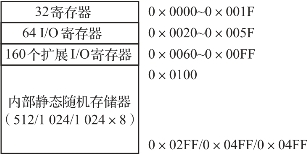

数据存储器映像图(图4-23)给出了ATmega48/88/168 SRAM空间的组织结构。ATmega48/88/168是一个复杂的微控制器,其支持的外设要比预留的64个I/O(通过IN/OUT指令访问)所能支持的要多。对于扩展的I/O空间段0x60~0xFF只能使用ST/STS/STD和LD/LDS/LDD指令。前768/1 280/1 280个数据存储器包括了寄存器文件、I/O存储器、扩展的I/O存储器以及数据SRAM。起始的32个地址为寄存器文件,然后是64个I/O存储器,接着是160个扩展I/O存储器,最后是512/1 024/1 024 B的数据SRAM。数据存储器的寻址方式分为5种:直接寻址、带偏移量的间接寻址、间接寻址、预减间接寻址和后加间接寻址。寄存器文件中的寄存器R26~R31为间接寻址的指针寄存器。直接寻址范围可达整个数据区。带偏移量的间接寻址模式能够寻址到由寄存器Y和Z给定的基址附近的63个地址。在自动预减和后加的间接寻址模式中,寄存器X、Y和Z自动增加或减少。ATmega48/88/168的全部32个通用寄存器、64个I/O寄存器、160个扩展I/O寄存器及512/1024/1 024 B的内部数据SRAM可以通过所有上述的寻址模式进行访问。

图4-22 程序存储器映像

图4-23 数据存储器映像图

2.EEPROM数据存储器

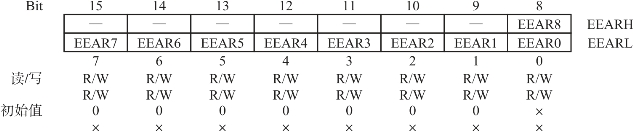

ATmega48/88/168包含256/512/512 B的EEPROM数据存储器。它是作为一个独立的数据空间而存在的,可以按字节读写。EEPROM的寿命至少为100 000次擦除周期。EEP-ROM的访问由地址寄存器、数据寄存器和控制寄存器决定。EEPROM的访问寄存器位于I/O空间。EEPROM的写访问时间由Table 3给出。自定时功能可以让用户监测何时开始写下一字节。如果用户要操作EEPROM,应当注意如下问题:在电源滤波时间常数比较大的电路中,上电/下电时V CC上升/下降速度会比较慢。此时CPU将工作于低于晶振所要求的电源电压。为了防止无意识的EEPROM写操作,在写EEPROM时需要执行一个特定的写时序。当执行EEPROM读操作时,CPU会停止工作4个周期,然后再执行后续指令;当执行EEPROM写操作时,CPU会停止工作2个周期,然后再执行后续指令。EEPROM地址寄存器——EEARH和EEARL如图4-24所示。

图4-24 EEPROM地址寄存器——EEARH和EEARL

(1)Bit15~Bit9 es:保留。保留位,读操作返回值为零。

(2)Bit 8~Bit 0——EEAR8 EAR~0:EEPROM地址。EEPROM地址寄存器——EARH和EEARL指定了256/512/512 B的EEPROM空间。EEPROM地址是线性的,从0到255/511/511。EEAR的初始值没有定义。在访问如图4-25所示的寄存器时,EEP-ROM之前必须为其赋予正确的数据。EEAR8在ATmega48中为无效位,必须始终将其赋值为“0”。

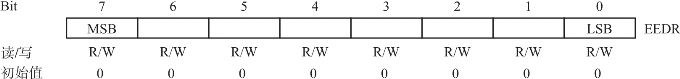

图4-25 EEPROM数据寄存器——EDR

(3)Bits 7~Bit0——EDR7.0:EEPROM数据。如图4-26所示,对于EEPROM写操作,EEDR是需要写到EEAR单元的数据;对于读操作,EEDR是从地址EEAR读取的数据。

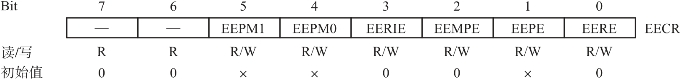

图4-26 EEPROM控制寄存器——EECR

(4)Bits 7、Bit6 es:保留。保留位,读操作返回值为零。

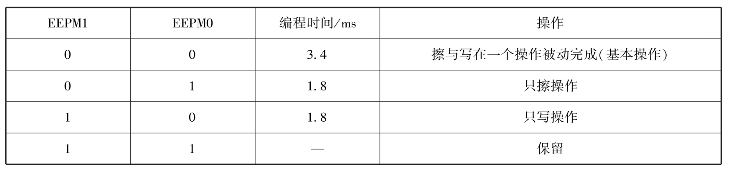

(5)Bit5,Bit4——EEPM1与EEPM0:EEPROM编程模式位。如表4-9所示,EEPROM编程模式位的设置决定对EEPE写入后将触发什么编程方式。EEPROM的编程可以作为一个基本操作来实现(擦除旧的数据并写入新的数据),也可以将擦除与写操作分为两步进行。不同编程模式的时序如表4-9所示。EEPE置位时,对EEPM n的任何写操作都将会被忽略。在复位过程中,除非EEPROM处于编程状态,EEPM n位将被设置为0b00。

表4-9 EEPROM编程模式位

(6)Bit3——EERIE:使能EEPROM就绪中断。若SREG的I为“1”,则置位EERIE使能EEPROM准备好中断。清零EERIE则禁止此中断,当EEWE清零时EEPROM准备好中断即可发生。

(7)Bit2——EEMPE:EEPROM主机写使能。EEMPE决定了EEPE置位是否可以启动EEPROM写操作。当EEMPE为“1”时,在4个时钟周期内置位EEPE把数据写入EEPROM的指定地址;若EEMPE为“0”,则操作EEPE不起作用。EEMPE置位后4个周期,硬件对其清零。见EEPROM写过程中对EEPE位的描述。(https://www.chuimin.cn)

(8)Bit 1——EEPE:EEPROM写使能。写使能信号EEPE是EEPROM的写入选通信号。当EEPROM数据和地址设置好之后,需置位EEPE以便将数据写入EEPROM。此时EEMPE必须置位,否则EEPROM写操作将不会发生。写时序如下(第3和第4步的次序可更改):

①等待EEPE为“0”。

②等待SPMCSR寄存器的SPMEN为零。

③将新的EEPROM地址写入EEAR(可选)。

④将新的EEPROM数据写入EEDR(可选)。

⑤对EECR寄存器的EEMPE写“1”,同时清零EEPE。

⑥在置位EEMPE之后的4个周期内置位EEPE。

在CPU写Flash存储器的时候不能对EEPROM进行编程。在启动EEPROM写操作之前软件必须检查Flash写操作是否已经完成。第2步仅在软件包含引导程序,允许CPU对Flash进行编程时才有用。如果CPU永远都不会写Flash,则第2步可以忽略。

注意:如有中断发生于步骤⑤和⑥之间,将导致写操作失败。因为此时EEPROM写使能操作将超时。如果一个操作EEPROM的中断打断了另一个EEPROM操作,EEAR或EE-DR寄存器可能被修改,引起EEPROM操作失败。建议此时关闭全局中断标志I。

经过写访问时间之后,EEPE硬件清零。用户可以凭此位判断写时序是否已经完成。EEPE置位后,CPU要停止两个时钟周期才会运行下一条指令。

(9)Bit 0——EERE:EEPROM读使能。读使能信号EERE是EEPROM的写入选通信号。当EEPROM地址设置好之后,需置位EERE以便将数据读入EEAR。EEPROM数据的读取只需要一条指令。读取EEPROM时CPU要停止4个时钟周期,然后才能执行下一条指令。用户在读取EEPROM时应该检测EEPE,如果一个写操作正在进行,就无法读取EEP-ROM,也无法改变寄存器EEAR。防止EEPROM数据丢失如果电源电压过低,CPU和EEP-ROM有可能工作不正常,造成EEPROM数据的毁坏(丢失)。这种情况在使用独立的EEP-ROM器件时也会遇到。由于电压过低造成EEPROM数据损坏有两种可能:一是电压低于EEPROM写操作所需要的最低电压;二是CPU本身已经无法正常工作。

EEPROM数据损坏的问题可以通过以下方法来避免:当电压过低时保持AVR RESET信号为低。这可以通过使能芯片的掉电检测电路BOD来实现。如果BOD电平无法满足要求,则可以使用外部复位电路。若写操作过程当中发生了复位,电源电压足够高,则写操作仍将正常结束。

(10)I/O存储器:ATmega48/88/168的所有I/O和外设都被放置在I/O空间。所有的I/O地址都可以通过LD/LDS/LDD和ST/STS/STD指令来访问,在32个通用工作寄存器和I/O之间传输数据。地址为0x00~0x1F的I/O寄存器还可用SBI和CBI指令直接进行位寻址,而SBIS和SBIC则用来检查单个位置位与否。使用IN和OUT指令时地址必须在0x00~0x3F。如果要像SRAM一样通过LD和ST指令访问I/O寄存器,相应的地址要加上0x20。

ATmega48/88/168是一个复杂的微处理器,其支持的外设要比预留的64个I/O(通过IN/OUT指令访问)所能支持的更多。对于扩展的I/O空间0x60~0xFF,只能使用ST/STS/STD和LD/LDS/LDD指令。为了与后续产品兼容,保留未用的位应写“0”,而保留的I/O寄存器则不应进行写操作。一些状态标志位的清除是通过写“1”来实现的。CBI和SBI指令可以操作I/O寄存器所有的位,并给置位的位回写“1”,因此会清除这些标志位。CBI和SBI指令只对0x00~0x1F的寄存器有效。

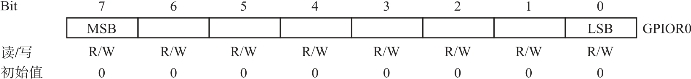

3.通用I/O寄存器

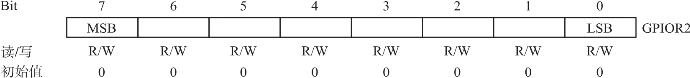

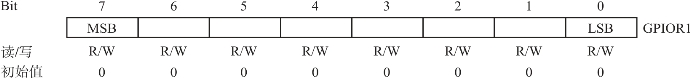

如图4-27~图4-29所示,ATmega48/88/168包含三个通用I/O寄存器。这些寄存器可以用来存储信息,尤其适合于存储全局变量与状态标志。位于0x00~0x1F的通用I/O寄存器可以通过SBI、CBI、SBIS与SBIC指令直接进行位寻址。

图4-27 通用I/O寄存器2——GPIOR2

图4-28 通用I/O寄存器1——GPIOR1

图4-29 通用I/O寄存器0——GPIOR0

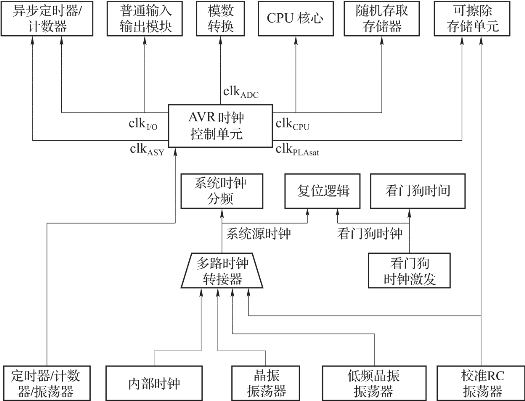

图4-30 AVR的主要时钟系统及其分布

相关文章

如图10-6所示为PROFIBUS电缆,包括100%的铝箔屏蔽和65%的镀锡铜编织网屏蔽,具有最大的屏蔽效果。图10-11 总线连接器的终端电阻图10-12 终端电阻的具体设置5.通信处理器与PROFIBUS相关联的通信处理器主要包括:1)CP 342-5通信处理器;2)CP 342-5 FO通信处理器;3)CP 443-5通信处理器;4)用于PC/PG的通信处理器。......

2025-09-29

在加载过程中,弹簧所吸收的能量称为变形能,以U 表示。对于自由放置的螺旋弹簧,在变形恢复时若没有与其他零件相摩擦,摩擦损失的能量等于零,则弹簧放出的能量和积蓄的能量相等。对于叠板弹簧、碟形弹簧及环形弹簧等,由于在过程中弹簧间变形相互摩擦,故有相当数量的摩擦功存在,致使卸载时的特性线低于加载时的特性线,如图3-35 所示。设计缓冲弹簧时,为保证其缓冲能力,应要求弹簧的变形能大于 被缓冲物体的动能。......

2025-09-29

根据《中华人民共和国能源法》第一百三十九条的法律术语解释,新能源是指“在新技术基础上开发利用的非常规能源,包括风能、太阳能、海洋能、地热能、生物质能、氢能、核聚变能、天然气水合物等”。清洁能源是指“环境污染物和二氧化碳等温室气体零排放或者低排放的一次能源,主要包括天然气、核电、水电及其他新能源和可再生能源等”。......

2025-09-29

2)时间分离将冲突双方在不同的时间段上分离,以降低解决问题的难度。如果冲突的一方可不按一个方向变化,则利用基于条件的分离原理解决冲突是可能的。......

2025-09-29

射频识别技术又称为无线射频识别,是一种无线通信技术,可以通过无线电信号识别特定目标并读写相关数据,识别系统与特定目标之间无须进行机械或光学接触。到2006年,空客有15个项目的赢利都得益于RFID技术。之后,空客公司决定在全公司范围内使用零件序列化的自动识别技术,增加飞机全生命周期的可视化,被称为价值链可视化计划,空客公司则称之为“空客业务雷达”。......

2025-09-29

Flash程序存储器分为引导程序区和应用程序区。在32个通用工作寄存器和I/O之间传输数据。不同的外部存储器可以设置不同的等待状态。......

2025-09-29

标准RAM图2-8 存储器结构存储文件寄存器和局部软元件等的数据。标准ROM存储进行ROM运行时的参数、程序等数据。表2-5 各类外置存储卡的使用功能(续)3.电池电池安装在CPU模块中,用于在发生电源故障的情况下,保持住程序内存、标准RAM和锁存软元件中的数据。表2-6 电池Q6BAT在常见CPU模块中的寿命值注意,存储卡和电池的安装和更换方法请参照QCPU用户手册。......

2025-09-29

表3-1 S7-1200PLC的存储区装载存储器装载存储器用于非易失性地存储用户程序、数据和组态。如果未插入存储卡,CPU将使用内部装载存储器;如果插入了存储卡,CPU将使用该存储卡作为装载存储器。CPU会将一些项目内容从装载存储器复制到工作存储器中。该易失性存储区将在断电后丢失,而在恢复供电时由CPU恢复。S7-1200 PLC的CPU的系统存储器分为表3-2所示的地址区。......

2025-09-29

相关推荐