SJA1000在软件和引脚上都是与它的前一款———PCA82C200独立控制器兼容的。在SJA1000的控制寄存器中没有SYNC位。像在PCA82C200中一样,写一个0~7之间的值,就将进入BasicCAN模式。SJA1000被设计为全面支持CAN 2.0B协议,这说明在处理扩展帧的同时,亦实现了扩展振荡器容差。SJA1000的主要新功能:1)接收、发送标准帧和扩展帧格式信息。......

2023-11-22

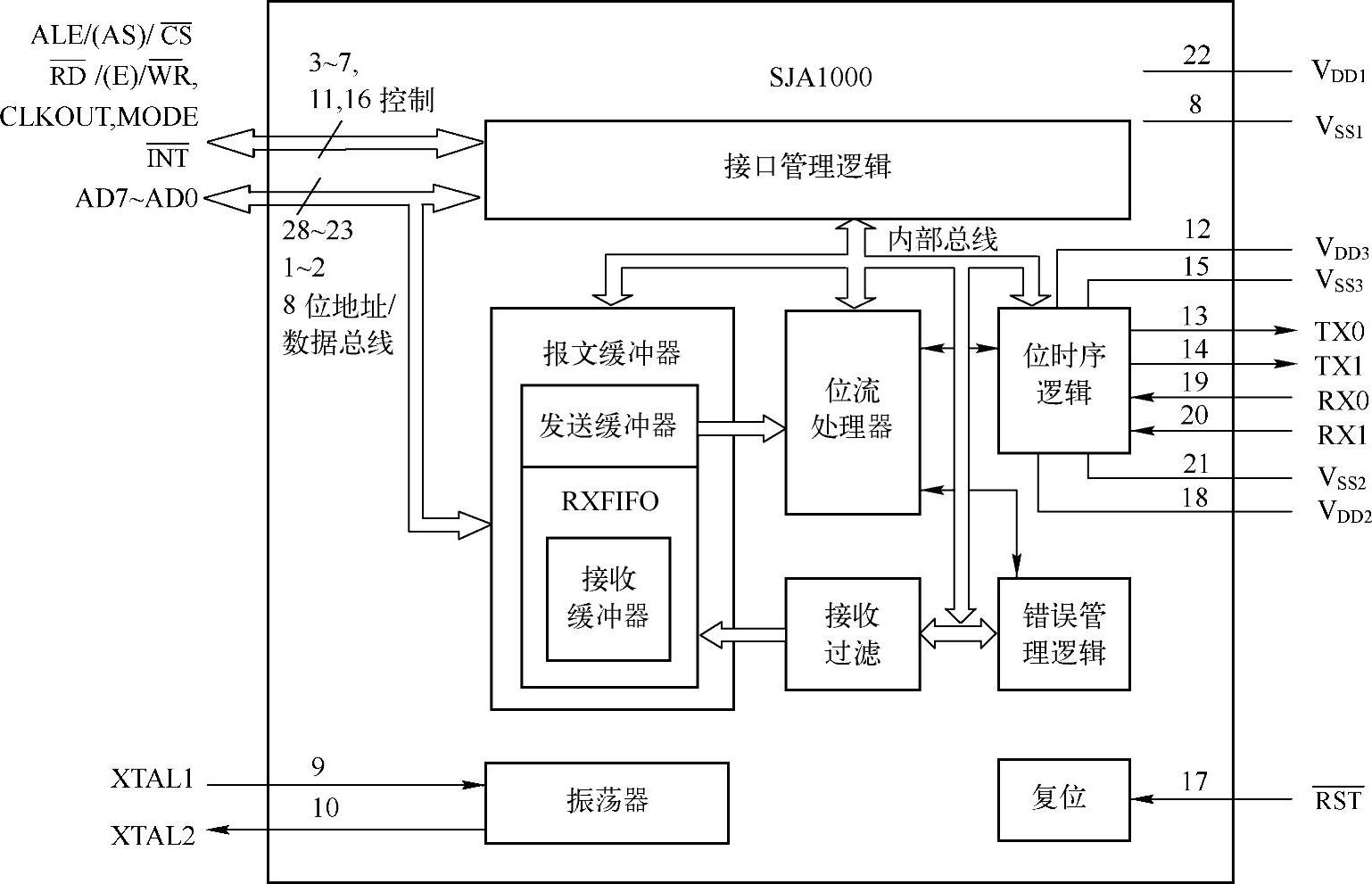

SJA1000的内部结构如图4-16所示。

SJA1000 CAN控制器主要由以下几部分构成。

1.接口管理逻辑(IML)

接口管理逻辑解释来自CPU的命令,控制CAN寄存器的寻址,向主控制器提供中断信息和状态信息。

2.发送缓冲器(TXB)

发送缓冲器是CPU和BSP(位流处理器)之间的接口,能够存储发送到CAN网络上的完整报文。缓冲器长13个字节,由CPU写入,BSP读出。

3.接收缓冲器(RXB,RXFIFO)

接收缓冲器是接收过滤器和CPU之间的接口,用来接收CAN总线上的报文,并存储接收到的报文。接收缓冲器(RXB,13B)作为接收FIFO(RXFIFO,64B)的一个窗口,可被CPU访问。

CPU在此FIFO的支持下,可以在处理报文的时候接收其他报文。

(www.chuimin.cn)

(www.chuimin.cn)

图4-16 SJA1000的内部结构框图

4.接收过滤器(ACF)

接收过滤器把它其中的数据和接收的标识符相比较,以决定是否接收报文。在纯粹的接收测试中,所有的报文都保存在RXFIFO中。

5.位流处理器(BSP)

位流处理器是一个在发送缓冲器、RXFIFO和CAN总线之间控制数据流的序列发生器。它还执行错误检测、仲裁、总线填充和错误处理。

6.位时序逻辑(BTL)

位时序逻辑监视串行CAN总线,并处理与总线有关的位定时。在报文开始,由隐性到显性的变换同步CAN总线上的位流(硬同步),接收报文时再次同步下一次传送(软同步)。BTL还提供了可编程的时间段来补偿传播延迟时间、相位转换(例如,由于振荡漂移)和定义采样点和每一位的采样次数。

7.错误管理逻辑(EML)

EML负责传送层中调制器的错误界定。它接收BSP的出错报告,并将错误统计数字通知BSP和IML。

有关现场总线及其应用技术的文章

SJA1000在软件和引脚上都是与它的前一款———PCA82C200独立控制器兼容的。在SJA1000的控制寄存器中没有SYNC位。像在PCA82C200中一样,写一个0~7之间的值,就将进入BasicCAN模式。SJA1000被设计为全面支持CAN 2.0B协议,这说明在处理扩展帧的同时,亦实现了扩展振荡器容差。SJA1000的主要新功能:1)接收、发送标准帧和扩展帧格式信息。......

2023-11-22

现场总线仪表圆卡可以连接各种传感器、执行器等,并将测量值通过串行协议传递给通信圆卡或者接收圆卡的数据进行输出。同时提供与各种传感器连接的仪表卡,构成了完整的现场总线仪表方案。NCS-RC105F可以与多种传统仪表连接组成FF协议智能仪表,是符合FF H1现场总线通信协议的仪表圆卡,如图1-14所示。NCS-RC105F仪表圆卡的特点如下:1)总线供电,总线电流<15 mA。图1-14 NCS-RC105F现场总线仪表圆卡图1-15 NCS-RC105F FF现场总线压力变送器套件......

2023-11-22

SJA1000是一种独立控制器,用于汽车和一般工业环境中的局域网络控制。它是PHIL-IPS公司的PCA82C200 CAN控制器的替代产品。而且,它增加了一种新的工作模式,这种模式支持具有很多新特点的CAN 2.0B协议,SJA1000具有如下特点:1)与PCA82C200独立CAN控制器引脚和电气兼容。4)与CAN 2.0B协议兼容。5)同时支持11位和29位标识符。7)PeliCAN模式扩展功能:①可读/写访问的错误计数器。④对每一个CAN总线错误的中断。⒀可编程的CAN输出驱动器配置。⒁增强的温度范围。......

2023-11-22

SJA1000为28引脚DIP和SO封装,引脚如图4-17所示。CS:片选输入,低电平允许访问SJA1000。CLKOUT:SJA1000产生的提供给微控制器的时钟输出信号;此时钟信号通过可编程分频器由内部晶振产生;时钟分频寄存器的时钟关闭位可禁止该引脚。......

2023-11-22

基金会现场总线,是在过程自动化领域得到广泛支持和具有良好发展前景的技术。屈于用户的压力,这两大集团于1994年9月合并,成立了现场总线基金会,致力于开发出国际上统一的现场总线协议。基金会现场总线分低速H1和高速H2两种通信速率。H1的传输速率为31.25 kbit/s,通信距离可达1900 m,可支持总线供电,支持本质安全防爆环境。H2总线标准也已形成。......

2023-11-22

PCI总线是由Intel公司提出的。PCI总线不是由ANSI通过的标准,但由于它是由厂家自发制定执行的标准,具有众多的优点,拥护者,执行者众多,成了事实上的标准。PCI总线共有100个引脚,如果只作为目标设备,至少需要47条,如作为主设备则需要49条。本设计使用位命令字,其定义如下:3.PCI总线基本协议PCI上的基本总线传输机制是突发成组传输。......

2023-11-22

INTERBUS定义了该模型的第1、2、7层。INTERBUS具有强大的可靠性、可诊断性和易维护性。INTERBUS采用了集总帧型的数据环通信。强大的诊断功能是INTERBUS区别于其他总线所独有的。INTERBUS CLUB负责向设备生产厂家提供INTERBUS的接口方案和接口芯片,向其成员提供信息,帮助解决技术问题及为特定的应用找寻合适的INTERBUS产品。INTERBUS的技术发起人为德国菲尼克斯公司。另外,在美国和中国也设有INTERBUS技术中心。......

2023-11-22

WorldFIP技术硬件体系由两个互补的部分组成:通信控制器和通信介质器件。5)用于WorldFIP连接的费用要求。WorldFIP现场总线第一个通信控制器是在1987年开发成功的。图8-9 WorldFIP现场总线通信站的连接......

2023-11-22

相关推荐