1971日本从美国引进了这项新技术,很快研制出了日本第一台PLC。总之,PLC是一台计算机,它是专为工业环境应用而设计制造的计算机,具有丰富的输入、输出接口,并且具有较强的驱动能力。......

2023-06-18

PCI设备对可Cache的存储器空间进行DMA读写操作的过程较为复杂,有关Cache Memory的话题可以独立成书。而不同的处理器系统使用的Cache Memory的层次结构和访问机制有较大的差异,这部分内容也是现代处理器系统设计的重中之重。

本节仅介绍在Cache Memory系统中与PCI设备进行DMA操作相关的一些最为基础的概念。在多数处理器系统中,使用了以下概念描述Cache一致性的实现过程。

1.Cache一致性协议

多数SMP处理器系统使用了MESI协议处理多个处理器之间的Cache一致性。该协议也称为Illinois protocol,在SMP处理器系统中得到了广泛的应用。MESI协议使用四个状态位描述每一个Cache行。

●M(Modified)位。M位为1时表示当前Cache行中包含的数据与存储器中的数据不一致,而且它仅在本CPU的Cache中有效,不在其他CPU的Cache中存在副本,在这个Cache行的数据是当前处理器系统中最新的数据副本。当CPU对这个Cache行进行替换操作时,必然会引发系统总线的写周期,将Cache行中数据与内存中的数据同步。

●E(Exclusive)位。E位为1时表示当前Cache行中包含的数据有效,而且该数据仅在当前CPU的Cache中有效,而不在其他CPU的Cache中存在副本。在该Cache行中的数据是当前处理器系统中最新的数据副本,而且与存储器中的数据一致。

●S(Shared)位。S位为1表示Cache行中包含的数据有效,而且在当前CPU和至少其他一个CPU中具有副本。在该Cache行中的数据是当前处理器系统中最新的数据副本,而且与存储器中的数据一致。

●I(Invalid)位。I位为1表示当前Cache行中没有有效数据或者该Cache行没有使能。MESI协议在进行Cache行替换时,将优先使用I位为1的Cache行。

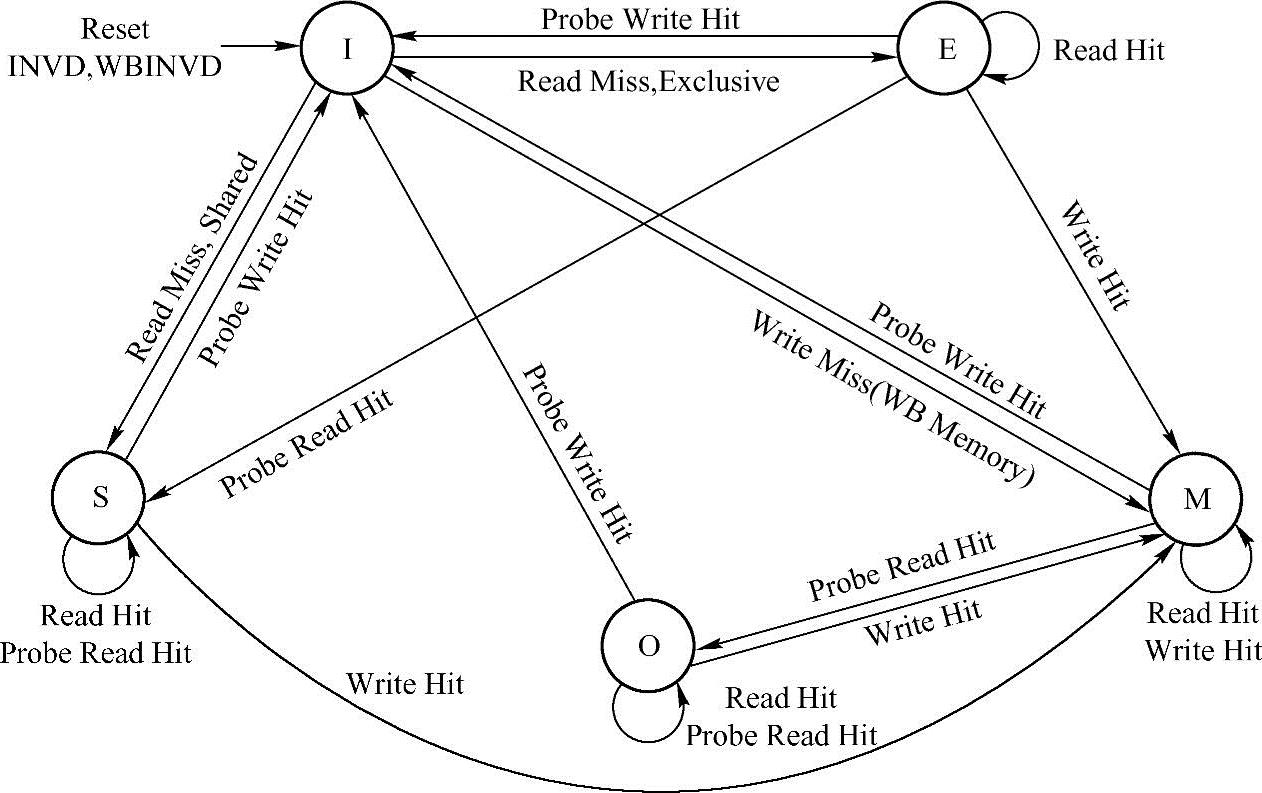

MESI协议还存在一些变种,如MOESI协议和MESIF协议。基于MOESI协议的Cache一致性模型如图3-5所示。AMD处理器就使用MOESI协议。不同的处理器在实现MOESI协议时,状态机的转换原理类似,但是在处理上仍有较大的区别。

图3-5 基于MOESI协议的Cache一致性模型

MOESI协议引入了一个O(Owned)状态,并在MESI协议的基础上,重新定义了S状态,而E、M和I状态和MESI协议的对应状态相同。

●O位。O位为1表示在当前Cache行中包含的数据是当前处理器系统最新的数据副本,而且在其他CPU中一定具有该Cache行的副本,其他CPU的Cache行状态为S。如果主存储器的数据在多个CPU的Cache中都具有副本时,有且仅有一个CPU的Cache行状态为O,其他CPU的Cache行状态只能为S。与MESI协议中的S状态不同,状态为O的Cache行中的数据与存储器中的数据并不一致。

●S位。在MOESI协议中,S状态的定义发生了细微的变化。当一个Cache行状态为S时,其包含的数据并不一定与存储器一致。如果在其他CPU的Cache中不存在状态为O的副本时,该Cache行中的数据与存储器一致;如果在其他CPU的Cache中存在状态为O的副本时,Cache行中的数据与存储器不一致。

在一个处理器系统中,主设备(CPU或者外部设备)进行存储器访问时,将试图从存储器系统(主存储器或者其他CPU的Cache)中获得最新的数据副本。如果该主设备访问的数据没有在本地命中时,将从其他CPU的Cache中获取数据,如果这些数据仍然没有在其他CPU的Cache中命中,主存储器将提供数据。外设设备进行存储器访问时,也需要进行Cache共享一致性。

在MOESI模型中,“Probe Read”表示主设备从其他CPU中获取数据副本的目的是为了读取数据;而“Probe Write”表示主设备从其他CPU中获取数据副本的目的是为了写入数据;“Read Hit”和“Write Hit”表示主设备在本地Cache中获得数据副本;“Read Miss”和“Write Miss”表示主设备没有在本地Cache中获得数据副本;“Probe Read Hit”和“Probe Write Hit”表示主设备在其他CPU的Cache中获得数据副本。

本节为简便起见,仅介绍CPU进行存储器写和与O状态相关的Cache行状态迁移,CPU进行存储器读的情况相对较为简单,请读者自行分析这个过程。

当CPU对一段存储器进行写操作时,如果这些数据在本地Cache中命中时,其状态可能为E、S、M或者O。

●状态为E或者M时,数据将直接写入到Cache中,并将状态改为M。

●状态为S时,数据将直接写入到Cache中,并将状态改为M,同时其他CPU保存该数据副本的Cache行状态将从S或者O迁移到I(Probe Write Hit)。

●状态为O时,数据将直接写入到Cache中,并将状态改为M,同时其他CPU保存该数据副本的Cache行状态将从S迁移到I(Probe Write Hit)。

当CPU A对一段存储器进行写操作时,如果这些数据没有在本地Cache中命中时,而在其他CPU,如CPU B的Cache中命中时,其状态可能为E、S、M或者O。其中CPU A使用CPU B在同一个Cache共享域中。

●Cache行状态为E时,CPU B将该Cache行状态改为I;而CPU A将从本地申请一个新的Cache行,将数据写入,并该Cache行状态更新为M。

●Cache行状态为S时,CPU B将该Cache行状态改为I,而且具有同样副本的其他CPU的Cache行也需要将状态改为I;而CPU A将从本地申请一个Cache行,将数据写入,并该Cache行状态更新为M。

●Cache行状态为M时,CPU B将原Cache行中的数据回写到主存储器,并将该Cache行状态改为I;而CPU A将从本地申请一个Cache行,将数据写入,并该Cache行状态更新为M。

●Cache行状态为O时,CPU B将原Cache行中的数据回写到主存储器,并将该Cache行状态改为I,具有同样数据副本的其他CPU的Cache行也需要将状态从S更改为I;

CPU A将从本地申请一个Cache行,将数据写入,并该Cache行状态更新为M。

Cache行状态可以从M迁移到O。例如当CPU A读取的数据从CPU B中命中时,如果在CPU B中Cache行的状态为M时,将迁移到O,同时CPU B将数据传送给CPU A新申请的Cache行中,而且CPU A的Cache行状态将被更改为S。

当CPU读取的数据在本地Cache中命中,而且Cache行状态为O时,数据将从本地Cache获得,并不会改变Cache行状态。如果CPU A读取的数据在其他Cache中命中,如在CPU B的Cache中命中而且其状态为O时,CPU B将该Cache行状态保持为O,同时CPU B将数据传送给CPU A新申请的Cache行中,而且CPU A的Cache行状态将被更改为S。

在某些应用场合,使用MOESI协议将极大提高Cache的利用率,因为该协议引入了O状态,从而在发送Read Hit的情况时,不必将状态为M的Cache回写到主存储器,而是直接从一个CPU的Cache将数据传递到另外一个CPU。目前MOESI协议在AMD和RMI公司的处理器中得到了广泛的应用。

Intel提出了另外一种MESI协议的变种,即MESIF协议,该协议与MOESI协议有较大的不同,也远比MOESI协议复杂,该协议由Intel的QPI(QuickPath Interconnect)技术引入,其主要目的是解决“基于点到点的全互连处理器系统”的Cache共享一致性问题,而不是“基于共享总线的处理器系统”的Cache共享一致性问题。(www.chuimin.cn)

在基于点到点互连的NUMA(Non-Uniform Memory Architecture)处理器系统中,包含多个子处理器系统,这些子处理器系统由多个CPU组成。如果这个处理器系统需要进行全机Cache共享一致性,该处理器系统也被称为ccNUMA(Cache Cohenrent NUMA)处理器系统。MESIF协议主要解决ccNUMA处理器结构的Cache共享一致性问题,这种结构通常使用目录表,而不使用总线监听处理Cache的共享一致性。

MESIF协议引入了一个F(Forward)状态。在ccNUMA处理器系统中,可能在多个处理器的Cache中存在相同的数据副本,在这些数据副本中,只有一个Cache行的状态为F,其他Cache行的状态都为S。Cache行的状态位为F时,Cache中的数据与存储器一致。

当一个数据请求方读取这个数据副本时,只有状态为F的Cache行,可以将数据副本转发给数据请求方,而状态位为S的Cache不能转发数据副本。从而MESIF协议有效解决了在ccNUMA处理器结构中,所有状态位为S的Cache同时转发数据副本给数据请求方,而造成的数据拥塞。

在ccNUMA处理器系统中,如果状态位为F的数据副本,被其他CPU复制时,F状态位将会被迁移,新建的数据副本的状态位将为F,而老的数据副本的状态位将改变为S。当状态位为F的Cache行被改写后,ccNUMA处理器系统需要首先Invalidate状态位为S其他的Cache行,之后将Cache行的状态更新为M。

独立地研究MESIF协议并没有太大意义,该协议由Boxboro-EX处理器系统[38]引入,目前Intel并没有公开Boxboro-EX处理器系统的详细设计文档。MESIF协议仅是解决该处理器系统中Cache一致性的一个功能,该功能的详细实现与QPI的Protocal Layer相关,QPI由多个层次组成,而Protocal Layer是QPI的最高层。

对MESIF协议QPI互连技术有兴趣的读者,可以在深入理解“基于目录表的Cache一致性协议”的基础上,阅读Robert A.Maddox,Gurbir Sin gh and Robert J.Safra nek合著的书籍“Weaving High Performance Multiprocessor Fabric”以了解该协议的实现过程和与QPI互连技术相关的背景知识。

值得注意的是,MESIF协议解决主要的问题是ccNUMA架构中SMP子系统与SMP子系统之间Cache一致性。而在SMP处理器系统中,依然需要使用传统的MESI协议。Nehalem EX处理器也可以使用MOESI协议进一步优化SMP系统使用的Cache一致性协议,但是并没有使用该协议。

为简化起见,本章假设处理器系统使用MESI协议进行Cache共享一致性,而不是MOESI协议或者MESIF协议。

2.HIT#和HITM#信号

在SMP处理器系统中,每一个CPU都使用HIT#和HITM#信号反映HOST主桥访问的地址是否在各自的Cache中命中。当HOST主桥访问存储器时,CPU将驱动HITM#和HIT#信号,其描述如表3-1所示。

表3-1 HITM#和HIT#信号的含义

HIT#和HITM#信号是FSB中非常重要的两个信号,各个CPU的HIT#和HITM#信号通过“线与”方式直接相连[39]。而在一个实际FSB中,还包括许多信号,本节并不会详细介绍这些信号。

3.Cache一致性协议中使用的Agent

在处理器系统中,与Cache一致性相关的Agent如下所示。

●Request Agent。FSB总线事务的发起设备。在本节中,Request Agent特指HOST主桥。实际上在FSB总线上的其他设备也可以成为Request Agent,但这些Request Agent并不是本节的研究重点。Request Agent需要进行总线仲裁后,才能使用FSB,在多数处理器的FSB中,需要对地址总线与数据总线分别进行仲裁。

●Snoop Agents。FSB总线事务的监听设备。Snoop Agents为CPU,在一个SMP处理器系统中,有多个CPU共享同一个FSB,此时这些CPU都是这条FSB上的Snoop Agents。Snoop Agents监听FSB上的存储器读写事务,并判断这些总线事务访问的地址是否在Cache中命中。Snoop Agents通过HIT#和HITM#信号向FSB通知Cache命中的结果。在某些情况下,Snoop Agents需要将Cache中的数据回写到存储器,同时为Request Agent提供数据。

●Response Agent。FSB总线事务的目标设备。在本节中,Response Agent特指存储器控制器。Response Agent根据Snoop Agents提供的监听结果,决定如何接收数据或者向Request Agent设备提供数据。在多数情况下,当前数据访问没有在Snoop Agents中命中时,Response Agent需要提供数据,此外Snoop Agents有时需要将数据回写到Re-sponse Agent中。

4.FSB的总线事务

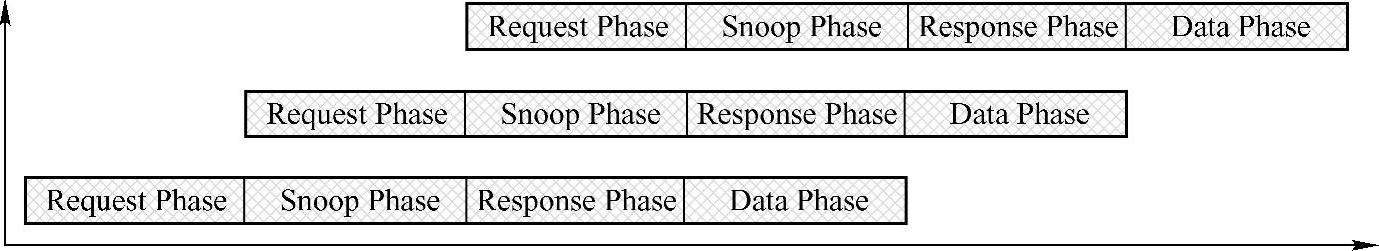

一个FSB的总线事务由多个阶段组成,包括Request Phase、Snoop Ph ase、Response Phase和Data Phase。目前在多数高端处理器中,FSB支持流水操作,即在同一个时间段内,不同的阶段可以重叠,如图3-6所示。

在一个实际的FSB中,一个总线事务还可能包含Arbitration Phase和Error Phase。而本节仅讲述图3-6中所示的4个基本阶段。

●Request Phase。Request Agent在获得FSB的地址总线的使用权后,在该阶段将访问数

据区域的地址和总线事务类型发送到FSB上。

图3-6 FSB的流水操作

●Snoop Phase。Snoop Agents根据访问数据区域在Cache中的命中情况,使用HIT#和HITM#信号,向其他Agents通知Cache一致性的结果。有时Snoop Agent需要将数据回写到存储器。

●Reponse Phase。Response Agent根据Request和Snoop Phase提供的信号,可以要求Re-quest Agent重试(Retry),或者Response Agent延时处理(Defer)当前总线事务。在FSB总线事务的各个阶段中,该步骤的处理过程最为复杂。本章将在下文结合PCI设备的DMA读写执行过程,说明该阶段的实现原理。

●Data Phase。一些不传递数据的FSB总线事务不包含该阶段。该阶段用来进行数据传递,包括Request Agent向Response Agent写入数据;Response Agent为Request Agent提供数据;和Snoop Agent将数据回写到Response Agent。

下面将使用本小节中的概念,描述在PCI总线中,与Cache相关的总线事务,并讲述相关的FSB的操作流程。

有关PCI Express体系结构导读的文章

1971日本从美国引进了这项新技术,很快研制出了日本第一台PLC。总之,PLC是一台计算机,它是专为工业环境应用而设计制造的计算机,具有丰富的输入、输出接口,并且具有较强的驱动能力。......

2023-06-18

欲使异步电动机控制系统解耦,关键是要找出两个分别决定磁通和电磁转矩的独立控制量,而且必须求出这两个控制量和能直接测量及控制的定子坐标变量的关系。联邦德国Blaschke等学者在1971年提出的磁场定向型矢量变换控制首先实现了这种控制思想,应用这种矢量变换控制构成了一个磁通反馈的变频调速系统。......

2023-06-25

数据挖掘就是综合应用一系列先进的技术从大量数据中提取人们感兴趣的信息和知识,它们是隐含的、事先未知且潜在有用的概念、规则、规律及模式等。这个概念诠释了数据挖掘的3个要点:数据挖掘要处理的数据量是巨大的。因此,高效率常常是数据挖掘算法研究的目标。4)数据转换:数据要被转换和整理,使其符合挖掘程序的格式。图2.1典型的数据挖掘系统构架......

2023-06-16

构图中的一致性表明同一空间范围内两个以上元素的属性相同,当同一空间中出现两个以上元素时,则一定存在相对位置的差别。建筑立面的均匀开窗,建筑结构中的均匀柱网都是建筑构件的一致性表达。该建筑中的一致性仅限于建筑外部形态,室内为一联通的大型办公空间。因此其空间、功能和结构均不包含一致性原则。......

2023-08-24

第一节边坡稳定的基本概念露天开采时,通常是把矿岩划成一定厚度的水平层,自上而下逐层开采。最终边坡角是指最终边坡面与水平面之间的夹角。各台阶参数的组合决定了最终边坡角的大小,而最终边坡又受到岩体的工程地质条件和开采深度的限制。露天矿边坡的稳定性随着开采作业的进行不断发生变化。当两组或两组以上结构面组合交线的倾向与边坡相近,倾角小于坡面角而大于结构面上的内摩擦角时,容易发生这类滑动。......

2024-07-05

事故是指在生产过程中,造成人员伤亡、财产损失或者其他损失的意外事件。隐患是指未被事先识别或未采取必要的风险控制措施,可能直接或间接导致事故的根源。安全技术措施是指以保障职工安全、防止伤亡事故为目的,在技术上所采取的措施。特种作业是指容易发生事故,对操作者本人、他人的安全健康及设备、设施的安全可能造成重大危害的作业。......

2023-08-23

交流电流有效值:对于正弦交流电流,则有:对于我国民用正弦交流电,220V是该正弦交流电压有效值,是其幅值。与频率、周期的关系:我国民用正弦交流电,称为“工频”:f=50Hz,T=0.02s,ω=100πrad/s≈314rad/s。两个同频率正弦量之间的相位之差,称为相位差。设正弦电压,用相量表示:或。图2-2 正弦量相量图......

2023-11-24

下面就以果汁厂的果汁生产为例对配方的基本结构进行说明。配方视图始终是过程画面的一部分。图7-29 配方中的数据流整体示意图2.在HMI设备和PLC之间传送配方值在配方视图和PLC之间传送完整的配方数据。组态时,通过设置“与PLC同步”功能来决定配方视图里的值与配方变量值同步。......

2023-06-15

相关推荐